terostechnology / vscode-teroshdl Goto Github PK

View Code? Open in Web Editor NEWVHDL and Verilog/SV IDE: state machine viewer, linter, documentation, snippets... and more!

Home Page: https://terostechnology.github.io/terosHDLdoc/

VHDL and Verilog/SV IDE: state machine viewer, linter, documentation, snippets... and more!

Home Page: https://terostechnology.github.io/terosHDLdoc/

Whenever I click on Generate template, I get an error notification:

Select a valid file.!

Also, I can't see any diagrams in Module documentation preview.

Ubuntu 20.04

Visual Studio Code 1.48.2 (Snap)

Python 3.8.2

hello,

is there is a way to add the xilinx libs to the project and my own custom packages that i use under work lib ?

the linter keeps showing errors about it

thanks

I try to generate module documentation, but module documentation window remains empty.

i see in debug console:

console.ts:137 [Extension Host] TypeError: Cannot read property 'substr' of undefined at tsVerilogParser.extractData (/home/anton/.vscode/extensions/teros-technology.teroshdl-0.0.3/node_modules/jsteros/src/parser/tsVerilogParser.js:338:42) at tsVerilogParser.getComments (/home/anton/.vscode/extensions/teros-technology.teroshdl-0.0.3/node_modules/jsteros/src/parser/tsVerilogParser.js:222:48) at tsVerilogParser.getGenerics (/home/anton/.vscode/extensions/teros-technology.teroshdl-0.0.3/node_modules/jsteros/src/parser/tsVerilogParser.js:243:25) at tsVerilogParser.getAll (/home/anton/.vscode/extensions/teros-technology.teroshdl-0.0.3/node_modules/jsteros/src/parser/tsVerilogParser.js:54:26) at async Documenter._get_code_tree (/home/anton/.vscode/extensions/teros-technology.teroshdl-0.0.3/node_modules/jsteros/src/documenter/documenter.js:290:21) at async Documenter._get_html_from_code (/home/anton/.vscode/extensions/teros-technology.teroshdl-0.0.3/node_modules/jsteros/src/documenter/documenter.js:153:21) at async Documenter.get_html (/home/anton/.vscode/extensions/teros-technology.teroshdl-0.0.3/node_modules/jsteros/src/documenter/documenter.js:71:20)

First of all a big thank you to the dev team, this extension looks very promising, especially the automated documentation generation!

On my machine I have a very recurring crash when I use terosHDL: "Extension host terminated unexpectedly"

The DevTools give me the following error:

c:\Users\user_name\.vscode\extensions\teros-technology.teroshdl-0.1.3\node_modules\jsteros\node_modules\web-tree-sitter\tree-sitter.js:1

(function (exports, require, module, __filename, __dirname) { var Module=void 0!==Module?Module:{};!function(e,t){"function"==typeof define&&define.amd?define([],t):"object"==typeof exports?module.exports=t():window.TreeSitter=t()}(0,function(){var e,t={};for(e in Module)Module.hasOwnProperty(e)&&(t[e]=Module[e]);var n,r,o=[],s="./this.program",i=function(e,t){throw t},a=!1,_=!1;a="object"==typeof window,_="function"==typeof importScripts,n="object"==typeof process&&"object"==typeof process.versions&&"string"==typeof process.versions.node,r=!a&&!n&&!_;var u,l,d,c,f="";n?(f=_?require("path").dirname(f)+"/":__dirname+"/",u=function(e,t){return d||(d=require("fs")),c||(c=require("path")),e=c.normalize(e),d.readFileSync(e,t?null:"utf8")},l=function(e){var t=u(e,!0);return t.buffer||(t=new Uint8Array(t)),O(t.buffer),t},process.argv.length>1&&(s=process.argv[1].replace(/\\/g,"/"))

[RuntimeError: abort(Error: spawn c:\Users\user_name\Watt\project_name\git ENOENT). Build with -s ASSERTIONS=1 for more info.

at process.we (c:\Users\user_name\.vscode\extensions\teros-technology.teroshdl-0.1.3\node_modules\jsteros\node_modules\web-tree-sitter\tree-sitter.js:1:11401)

at process.emit (events.js:228:7)

at processPromiseRejections (internal/process/promises.js:201:33)

at processTicksAndRejections (internal/process/task_queues.js:95:32)]

I'm using Windows 10

Could it be that it is looking for a git directory? Sadly I am not using git but subversion... :)

Thanks a lot!

dbhi/vsc-hdl is a placeholder/playground where I've been gathering references/ideas and trying features provided by VSCode Extensions to achieve a solution similar to the purpose of this repo. I think it would be desirable to add a brief explanation to the README referencing VUnit Test Explorer and hackfin.gitlab.io/xhdl, since both are projects that could be potentially integrated here.

Hi,

I have recently started using terosHDL in VSCode and would like to change the way begin-end is aligned. Currently there is a line break for "begin" like

if(a)

begin

...

end

but I prefer not to have line break before begin. i.e., something like this

if(a) begin

...

end

Is there a setting configuration for this?

If you hover over a variable, the declaration will not be visible.

Hi,

While terosHDL seems amazing (I just started testing it), It seems to lack an important feature which would be an "Instanciate Module" command. This command would let you select a module and generate an instanciation snippet, presenting all ports so the user only have to "connect" the wires.

You could also do that using the name of the file where the module is instanciated as done in Sublime Text 3 (https://sv-doc.readthedocs.io/en/latest/instance/)

This feature is, IMHO, a must-have, and it would be great to see it in terosHDL !

Best regards,

Julien FAUCHER

Given that TerosHDL already has Wavedrom support (which is awesome by the way!), there is a project authored by the same person that provide some neat diagrams in much the same way as Wavedrom is constructed. Would it be possible to support BitField in much the same way Wavedrom is supported already?

A way to see a BitField diagram in action would be to put to put the following text in the form at https://wavedrom.com/editor.html

{reg: [

{bits: 7, name: 'opcode', attr: 'OP-IMM'},

{bits: 5, name: 'rd', attr: 'dest'},

{bits: 3, name: 'func3', attr: ['ADDI', 'SLTI', 'SLTIU', 'ANDI', 'ORI', 'XORI'], type: 4},

{bits: 5, name: 'rs1', attr: 'src'},

{bits: 12, name: 'imm[11:0]', attr: 'I-immediate[11:0]', type: 3}

]}

if you add a wavedrom description before the module description, then the parser breaks

//! { signal: [

//! ['sink',

//! { name: 'ready', wave: '1........'},

//! { name: 'valid', wave: '01......0'},

//! { name: 'sop', wave: '010......'},

//! { name: 'eop', wave: '0......10'},

//! { name: 'empty[3:0]', wave: 'x3......x', data: 'empty[3:0]'},

//! { name: 'data[95:0]', wave: 'x4......x', data: 'data[95:0]'},

//! ],

//! {},

//! ['source',

//! { name: 'ready', wave: '1........'},

//! { name: 'valid', wave: '01......0'},

//! { name: 'sop', wave: '010......'},

//! { name: 'eop', wave: '0......10'},

//! { name: 'empty[3:0]', wave: 'x3......x', data: 'empty[3:0]'},

//! { name: 'data[127:0]', wave: 'x4......x', data: 'data[127:0]'},

//! ]

//! ]}

module conv_6to8 (

input reset_n, //! Don't used

input clk, //! Don't usedWithout wavedrom

The extension isn't able to find structs declared in another file using `include.

For the documentation of VHDL/V/SV, it would be nice if you can choose where this goes. Take the following example:

--! This is a description

--! of the entity.

entity counter is

port (

clk: in std_logic; --! Clock comment

out_data: out std_logic --! Description **port comment**

);

end counter;

I don't like documenting ports/generics in-line because it is a headache to deal with when instantiating an entity by copying/pasting the declaration. The other problem with commening generics/ports/subprogram parameters in-line is for anything complicated, it makes it really difficult to see what all is there because descriptions are more verbose. For complicated functionality in port/subprogram parameter relationships, this can become very ugly and hard to maintain. Instead, I propose that documentation allow the following format:

--! This is a description

--! of the entity.

--!

--! clk: comment

--! out_data : Description **port comment**

entity counter is

port (

clk: in std_logic;

out_data: out std_logic

);

end counter;

In this case, the documentation output should be the exact same where the parser looks for the name in the special comments above the entity and associates them with a port/generic when it sees the name of the port as the first part of the comment line string. This should apply to subprograms as well. For example, here is documentation I have for a VHDL procedure:

-- send_raw_data_packets

-- sends data packets to the driver formatted raw bytes. This will

-- construct and push packets to the driver queue and the number of packets

-- will depend on number of frames to send and number of bytes in each

-- frame

--

-- net : VUnit net global signal

-- rnd : RandomPType protected variable, init this outside prc

-- num_frames : Number of frames to send to UUT

-- min_num_bytes : min num of bytes

-- max_num_bytes : max num of bytes, this will randomly set number of

-- bytes in each frame constrained to this range

-- num_bytes_vec : integer_vector that will be used instead of random

-- num of bytes. If default or any 0's in vec, random

-- bytes used, else if this is non-zero and length1, all

-- frames will be the same num of bytes, else if length

-- > 1, this needs to be num_frames length and this is

-- how you can specify the number of bytes in each frame

procedure send_raw_data_packets (

signal net : inout network_t;

variable rnd : inout RandomPType;

num_frames : positive := 1;

min_num_bytes : positive := 1;

max_num_bytes : positive := 1;

num_bytes_vec : integer_vector := (0 => 0)

);

As you can see, it would be really ugly if I had to put the port descriptions in-line with each procedure port.

The other thing that would be nice is to have a way of grouping signals in the port/generic. E.g. adding something like

--! ~name~

--! <description for below signals/generics/parameters>

--! clk: comment

--!

--! ~name~

--! <description here for below signals/generics/parameters>

--! out_data : comment

In my VHDL file, the Wavedrome and Bitfield Modules will not be created if you write them inside the architecture. Togther with a Graphical HDL Entry tool like (HDL Works or HDL Designer) it's not possible to write code outside the architecture. In that case, it will be good if you can create wavedrome and bitfield modules inside the architechture.

I have generate a testbench for an i2c master (attached).

The resulting vunit testbench has a deferred constant which makes the compilation fail.

TerosHDL 0.1.0

If file extension ends with 'v' -- problems tab shows lines with 'TerosHDL:verible'

If the same file is renamed to have extension as 'sv' -- no lines with 'TerosHDL:verible' are shown anymore.

Direct call verible-verilog-lint shows the same output on 'v' files and 'sv' files as problems tab for 'v' files.

Expected that Verible should work with SystemVerilog files as well as Verilog

The diagram is empty when pdf documentation is generated

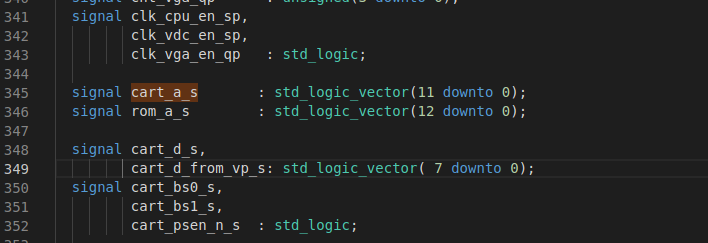

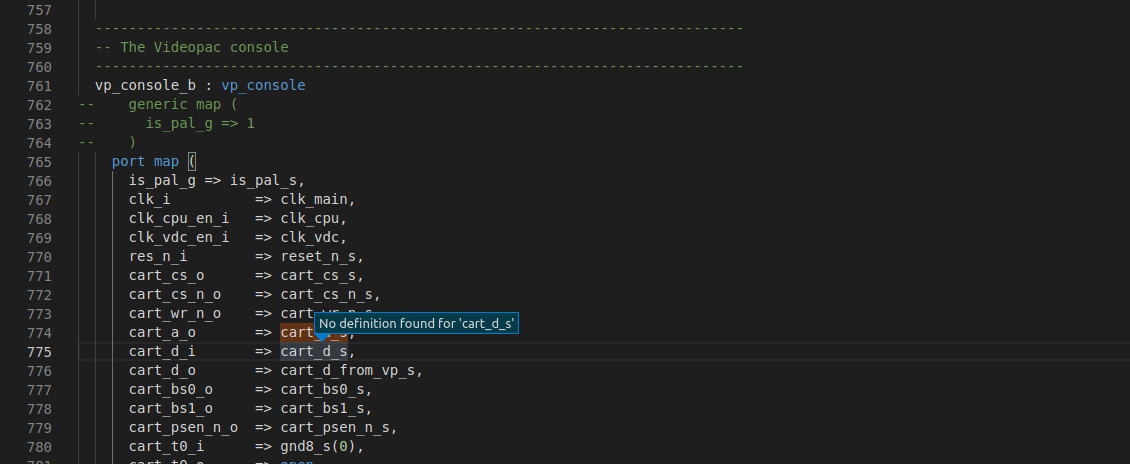

When referencing signals with a multiple declaration is not reconized, neither with Go to definition option (F12)

This is an example of declaration

The signal cart_a_s is well recognized:

The signal cart_d_s is not recognized:

My source code is a modification of this one https://github.com/yomboprime/VideoPac-ZXDOS/blob/master/src/board/ZX_Uno_xs6/ZX_Uno_xs6_vp.vhd with some changes, but the issue is already in that one.

Performanceteroshdl0.0.8Windows_NT x64 10.0.183631.52.1

c:\Users\azhak\AppData\Local\Temp\teros-technology.teroshdl-unresponsive.cpuprofile.txt

Find more details here: https://github.com/microsoft/vscode/wiki/Explain-extension-causes-high-cpu-load

If you define an "alias" in VHDL, the declaration will not be recognized / find by Hover and structure

Hi all,

thanks for sharing this project, it is really helpful.

It would be very interesting to have the possibility to easily format any SystemVerilog Code.

In the past I used the formatted from Sublime Text SystemVerilog Package and it works good:

https://github.com/TheClams/SystemVerilog

https://github.com/TheClams/SystemVerilog/blob/master/verilogutil/verilog_beautifier.py

It would be possible to integrate this formatter in TerosHDL for Visual Studio Code?

Thanks

After installing vscode-terosHDL, extension keep failed when typing in settings.json

I have installed v0.0.2 on a Linux Ubuntu 18.04.03 machine.

When I try to get the documentation of a VHDL module. I don't get it (no symbol, co comments).

Here is the developer tool log:

[Extension Host] Error: Command failed: python /home/lcolombini/.vscode/extensions/teros-technology.teroshdl-0.0.2/node_modules/jsteros/src/parser/parser.py "!" "/tmp/f-2020526-16125-1lt54i9.8xxak" at checkExecSyncError (child_process.js:634:11) at execSync (child_process.js:670:15) at electron/js2c/asar.js:696:23 at VhdlParser.getAll (/home/lcolombini/.vscode/extensions/teros-technology.teroshdl-0.0.2/node_modules/jsteros/src/parser/vunitVhdlParser.js:43:20) at Documenter._get_code_tree (/home/lcolombini/.vscode/extensions/teros-technology.teroshdl-0.0.2/node_modules/jsteros/src/documenter/documenter.js:265:34) at Documenter._get_html_from_code (/home/lcolombini/.vscode/extensions/teros-technology.teroshdl-0.0.2/node_modules/jsteros/src/documenter/documenter.js:150:32) at Documenter.get_html (/home/lcolombini/.vscode/extensions/teros-technology.teroshdl-0.0.2/node_modules/jsteros/src/documenter/documenter.js:70:31) at Object. (/home/lcolombini/.vscode/extensions/teros-technology.teroshdl-0.0.2/out/lib/documenter/documenter.js:64:53) at Generator.next () at fulfilled (/home/lcolombini/.vscode/extensions/teros-technology.teroshdl-0.0.2/out/lib/documenter/documenter.js:5:58)

Code : 1.46.0

Python2 : 2.7.17

Python3 : 3.6.9

Hello! I found that installation in isolated environment (not connected to internet) not works.

Plugin installed from XCI.

I've checked plugin installation folder - content almost matches to same folder on internet connected instance.

Plugin seems to be installed, but any action produces error. For example - for Tools configuration following error reported: command 'teroshdl_tree_view.config' not found

Would you please help to resolve it?

Hello,

i am so sorry but i have a very basic question: is this plugin available on the vscode marketplace. I am not able to find it... should it be installed manually ?

Thanks

Up until the latest release, Wavedrom & Bitfield were working as expected. In the latest release neither seem to show up in the doc viewer or the HTML doc I generated.

Note: Tried out the State machine viewer for ~ 10 state machines and it worked beautifully

A declarative, efficient, and flexible JavaScript library for building user interfaces.

🖖 Vue.js is a progressive, incrementally-adoptable JavaScript framework for building UI on the web.

TypeScript is a superset of JavaScript that compiles to clean JavaScript output.

An Open Source Machine Learning Framework for Everyone

The Web framework for perfectionists with deadlines.

A PHP framework for web artisans

Bring data to life with SVG, Canvas and HTML. 📊📈🎉

JavaScript (JS) is a lightweight interpreted programming language with first-class functions.

Some thing interesting about web. New door for the world.

A server is a program made to process requests and deliver data to clients.

Machine learning is a way of modeling and interpreting data that allows a piece of software to respond intelligently.

Some thing interesting about visualization, use data art

Some thing interesting about game, make everyone happy.

We are working to build community through open source technology. NB: members must have two-factor auth.

Open source projects and samples from Microsoft.

Google ❤️ Open Source for everyone.

Alibaba Open Source for everyone

Data-Driven Documents codes.

China tencent open source team.