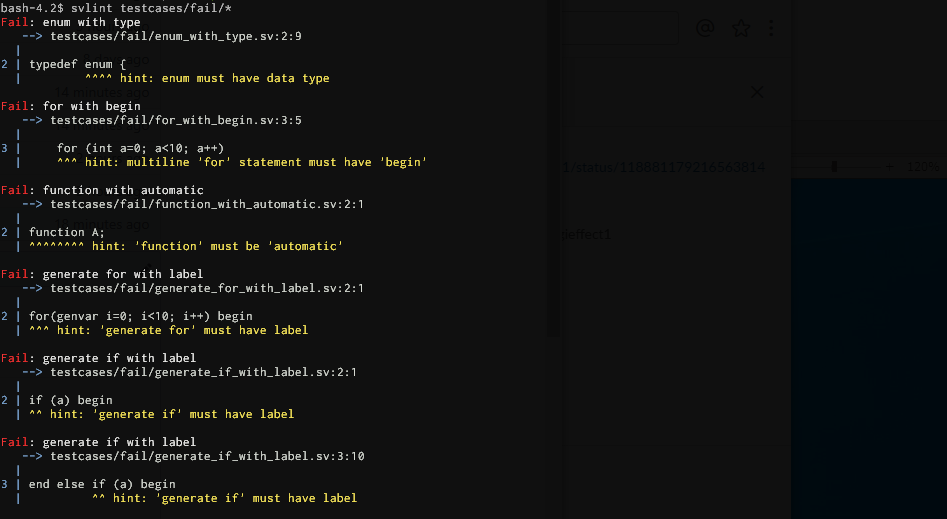

SystemVerilog linter compliant with IEEE1800-2017. Written in Rust, based on sv-parser. Svlint is also integrated with most text editors via svls.

svlint can be installed in several ways:

- Download a release,

extract, and add the

bin/directory to your$PATH. A PDF copy of the MANUAL is included in thedoc/directory. - If you have a Rust toolchain, then

you can install the binary with cargo, via

cargo install svlint. This will copy thesvlintbinary (and the dev-onlymdgenbinary) to (usually)~/.cargo/bin, but not the wrapper scripts (e.g.svlint-parseonly) or pre-written configurations (e.g.parseonly.toml) fromrulesets/. - snapcraft, via

sudo snap install svlint.

To see information about the command line interface use svlint --help,

and to see which version you're running use svlint --version.

Further information on how svlint works, how to configure it, and other usage information is in the manual.